# Examination WS 17/18 **Communication Systems and Protocols**

Institute for Information Processing Technologies - ITIV Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

#### Communication Systems and Protocols

Date: 13.02.2018 Name: Test Name Matr. ID: 1234567

ID: 1

Lecture Hall: ITIV Seat: 1

### Prerequisites for the examination

#### Aids:

- A single sheet of A4 paper with self- and hand-written notes. Writing may be on both sides

- A dictionary

- A non-programmable calculator.

- Writing utensils

- Use only indelible ink use of pencils and red ink is prohibited.

- Other material than that mentioned above, is strictly forbidden. This includes any type of communication to other people.

#### Duration of the examination:

The exam duration is 120 minutes.

#### **Examination documents:**

The examination comprises 30 pages (including title page, 8 blocks of tasks).

Answers may be given in English or German. A mix of language within a single (sub)-task is not allowed.

# Please check your matriculation number and id on every page before processing

In your solution mark clearly which part of the task you are solving. Do not write on the backside of the solution sheets. If additional paper is needed ask the examination supervisor.

End of Exam:

You will not be allowed to hand in your examination and leave the lecture hall in the last 30 minutes of the examination. At the end of the examination: Stay at your seat and put all sheets (including this title page) into the envelope. Only sheets in the envelope will be corrected. We will collect the examination.

|         |                                | Page | $\approx$ Pts. [%] | Points |

|---------|--------------------------------|------|--------------------|--------|

| Task 1: | Physical Basics                | 2    | 12                 |        |

| Task 2: | Transmission Principles        | 6    | 12                 |        |

| Task 3: | Modulation and Spread Spectrum | 10   | 11                 |        |

| Task 4: | Media Access                   | 15   | 12                 |        |

| Task 5: | Error Protection               | 18   | 12                 |        |

| Task 6: | Protocols                      | 21   | 12                 |        |

| Task 7: | Routing                        | 25   | 12                 |        |

| Task 8: | Network Topologies             | 28   | 13                 |        |

|         |                                |      |                    | $\sum$ |

# Task 1: Physical Basics

## Task 1.1: Drivers

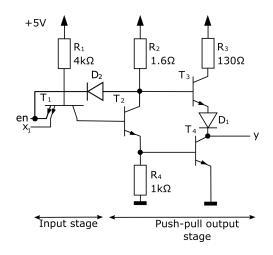

A) Insert the logic level (H/HIGH, L/LOW, Z/HIGH-IMPEDANCE) of the output and the state of the transistors (C/conducts, B/blocks) into the table according to the input configuration  $x_1$  and en at the tri-state TTL output driver.

Figure 1.1: Tri-state TTL output driver

| $x_1$ | en | $T_1$ | $T_2$ | $T_3$ | $T_4$ | y |

|-------|----|-------|-------|-------|-------|---|

| L     | L  |       |       |       |       |   |

| Н     | L  |       |       |       |       |   |

| L     | Н  |       |       |       |       |   |

| Н     | Н  |       |       |       |       |   |

| B) | List two advantages of using TTL drivers over open-collector drivers. |

|----|-----------------------------------------------------------------------|

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

|    |                                                                       |

## Task 1.2: AD Conversion

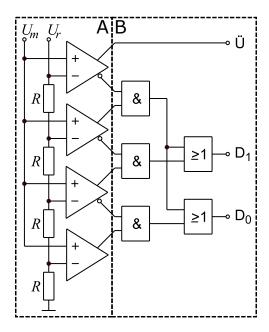

One way of implementing the AD-conversion is the flash converter. A 2-bit flash converter is shown in Figure 1.2.

Figure 1.2: Flash Converter

| A) | Briefly explain the the working principle of a flash converter. What happens in sections A and B? What is the purpose of the resistor cascade? |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

|    |                                                                                                                                                |

B) Name one advantage and one disadvantage of the flash converter.

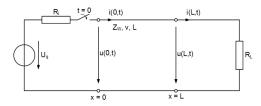

### Task 1.3: Reflections on wires

In figure 1.3 a transmission system is given. It consists of a voltage source of unknown voltage  $U_q$  (including an internal resistance  $R_i$ ), a signal line of length L and a resistor  $R_L$  as receiver. The signal propagates with speed v.

Figure 1.3: Transmission system

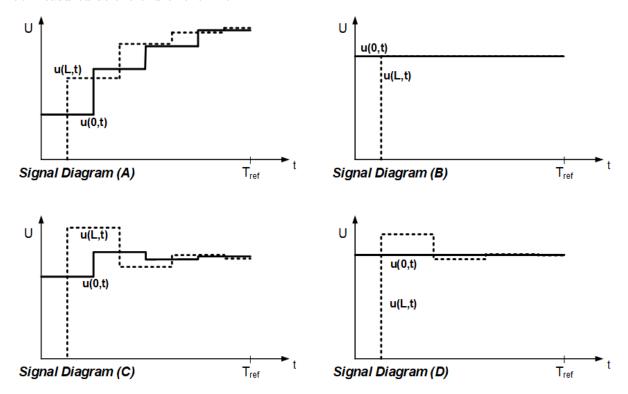

For varying  $R_i$  and  $R_L$  the following signal diagrams (figure 1.4) can be drawn. They are showing the voltage u(0,t) at the beginning of the signal line and the voltage u(L,t) that can be measured at the end of the line.

Figure 1.4: Voltages on signal line

| ,                                         | ich of the examples given le value of $R_L$ ? Justify yo |                                                         | ne line terminated correctly wit                                |

|-------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------|

| <ul><li> Is the</li><li> Is the</li></ul> | e reflection factor $r_L$ at th                          | e beginning of the signal<br>e end of the signal line r | line negative, positive, or zero                                |

| ( )                                       |                                                          | $r_i \text{ [neg, pos, 0, -]}$                          | $egin{array}{c} r_L \; [	ext{neg, pos, 0, -}] \end{array}$      |

|                                           | Signal diagram (A)                                       |                                                         |                                                                 |

|                                           | Signal diagram (B)                                       |                                                         |                                                                 |

|                                           | Signal diagram (C)                                       |                                                         |                                                                 |

|                                           | Signal diagram (D)                                       |                                                         |                                                                 |

| $R_L$ , and                               |                                                          | added to $R_L$ . Does this                              | . To terminate the line properly resisor have to be added in se |

| D) Calcu                                  | late $R_t$ such that the line                            | is properly terminated a                                | ssuming the values given above                                  |

# **Task 2: Transmission Principles**

## Task 2.1: Line Codes

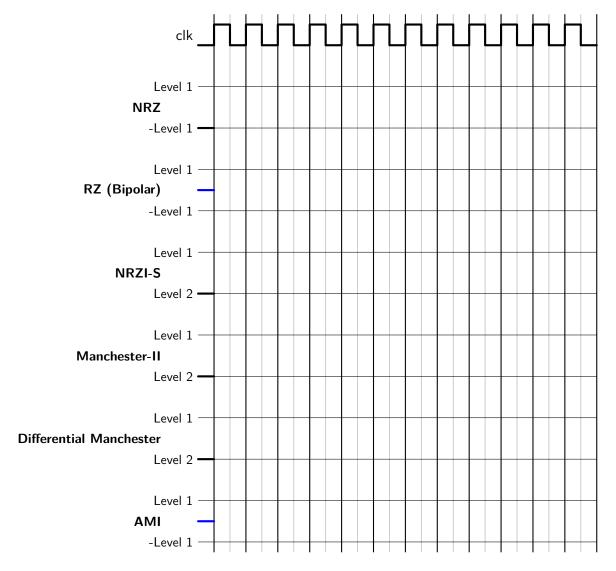

A) We want to transmit the bit string 1010 1110 0001 through a serial wire communication channel. Complete Figure 2.1 with the digital signals transmitted using each encoding scheme.

Figure 2.1: Line codes

| Mat | rNr.: 1234567 ID: 1                                                                                                                                                                                                       |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3)  | Manchester-II (Bipolar), Differential Manchester (Bipolar) and AMI are examples of codes that do not have DC components in their frequency spectrum. Explain why they present such a characteristic. Be concise.          |  |

| 2)  | Among the codes in Figure 2.1, Bipolar RZ, Differential Manchester and Manchester-II require a larger Bandwidth to transmit the same message. Explain why that happens. Be concise.                                       |  |

|     |                                                                                                                                                                                                                           |  |

| ))  | Given the transmission of a random sample signal, which codes in Figure 2.1 do not enable clock recovery of the transmitter's frequency? What is the common reason that prevents clock recovery in all codes? Be concise. |  |

|     |                                                                                                                                                                                                                           |  |

|     |                                                                                                                                                                                                                           |  |

### Task 2.2: $I^2C$ Arbitration

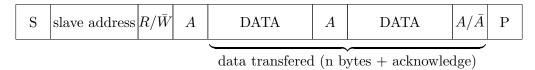

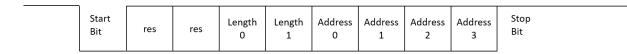

In this task we want to investigate the data transmission on the  $I^2C$ -Bus. The simplified packet format is given in Figure 2.2. Three master nodes are simultaneously trying to transmit or read one byte of data to or from different slaves over the  $I^2C$ -Bus.

| term          | descripion                   |

|---------------|------------------------------|

| S             | start condition              |

| slave address | 7-bit slave address          |

| $R/\bar{W}$   | read/write: read 1, write 0  |

| A             | acknowledge from slave ('0') |

| $ar{A}$       | not acknowledge ('1')        |

| DATA          | 8-bit data                   |

| P             | stop Condition               |

Figure 2.2: I<sup>2</sup>C-Bus frame format

| ps taken to perform the arbitration in an $I^2C$ multimaster interface? by step the process by which the arbitration is performed. |

|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                    |

|                                                                                                                                    |

| ultimaster configuration, what happens if two masters address the same r answer.                                                   |

|                                                                                                                                    |

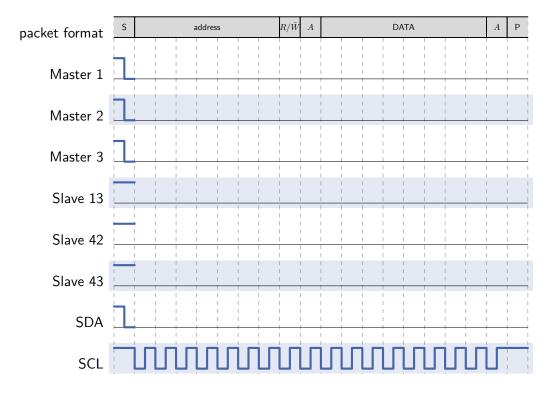

D) The addresses of the slaves, communication mode  $(R/\overline{W})$  and the data to be sent or read to or from them is shown in the Table 2.1. Complete the signal diagram in the Figure 2.3.

| node     | slave address | $R/\overline{W}$ | data     |

|----------|---------------|------------------|----------|

| Master 1 | 0001101       | 1                | 10101100 |

| Master 2 | 0101010       | 0                | 11001110 |

| Master 3 | 0101011       | 1                | 01010101 |

Table 2.1: I<sup>2</sup>C Communication Parameters

Figure 2.3: Signal sequence

| E) How | many nodes | can be connected | to the $I^2$ | C bus at | $\max imum?$ | Justify your | ${\it answer!}$ |

|--------|------------|------------------|--------------|----------|--------------|--------------|-----------------|

|--------|------------|------------------|--------------|----------|--------------|--------------|-----------------|

# Task 3: Modulation and Spread Spectrum

## Task 3.1: Modulation

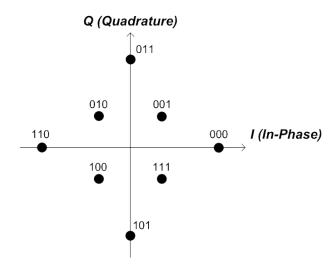

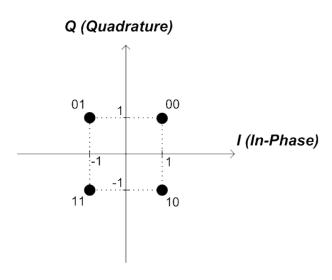

Figure 3.1: The constellation diagram of an unknown modulation

| A) | The constellation diagram of an unknown | n modulation is shown in the F | igure 3.1. Which |

|----|-----------------------------------------|--------------------------------|------------------|

|    | modulation scheme is used?              |                                |                  |

| B) | Assume that you have a bistream of information, i.e. 101011000111, which you want to |  |

|----|--------------------------------------------------------------------------------------|--|

|    | modulate using 256-Quadrature Amplitude Modulation (256-QAM) technique. How many     |  |

|    | bits does the 256-Quadrature Amplitude Modulator have to read for each symbol?       |  |

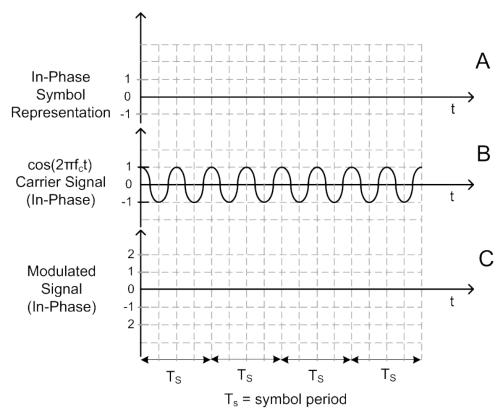

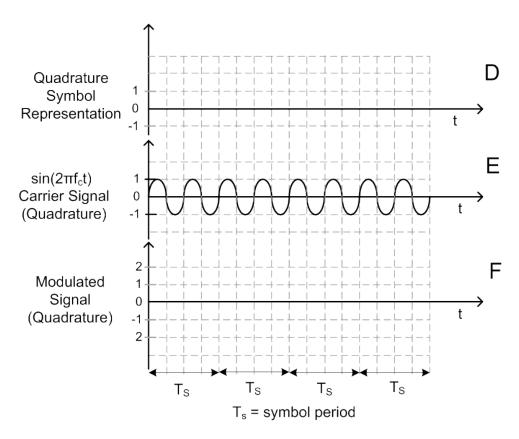

A constellation diagram of 4-QAM is shown below (Figure 3.2). You have information bits 11000110 which will be encoded starting from the left to the right. The Figure 3.3 shows the in-phase carrier signal (B), in-phase symbol (A), and in-phase modulated signal (C). Moreover, the Figure 3.4 shows the quadrature carrier signal (E), quadrature symbol (D), quadrature modulated signal (F). Use the Figure 3.3 (A and C) and Figure 3.4 (D and F) to sketch the waveforms of symbol representations and modulated information signals seen from in-phase and quadrature axes. The symbol period is twice as long as the period of carrier signal.

Figure 3.2: A constellation diagram of 4-QAM

Figure 3.3: In-Phase symbol representation, carrier signal (in-phase), and modulated signal (in-phase)

Figure 3.4: Quadrature symbol representation, carrier signal (quadrature), and modulated signal (quadrature)

## Task 3.2: Spread Spectrum

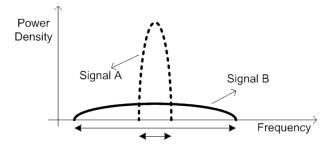

A) In Figure 3.5, the power density of a signal is given before and after the spread spectrum technique. The signal A represents the power density before spread and the signal B is after spread. What is the ratio between the area of signal A and the area of signal B?

Figure 3.5: A representation of signal's power density vs. signal's frequencies

B) Mention two main requirements for spreading codes used by CDMA.

| Node | Signal |    |    |    |    |    |    |    |

|------|--------|----|----|----|----|----|----|----|

| 0    | +1     | +1 | +1 | +1 | +1 | +1 | +1 | +1 |

| 1    | +1     | -1 | +1 | -1 | +1 | -1 | +1 | -1 |

| 2    | +1     | +1 | -1 | -1 | +1 | +1 | -1 | -1 |

| 3    | +1     | -1 | -1 | +1 | +1 | -1 | -1 | +1 |

| 4    | +1     | +1 | +1 | +1 | -1 | -1 | -1 | -1 |

| 5    | +1     | -1 | +1 | -1 | -1 | +1 | -1 | +1 |

| 6    | +1     | +1 | -1 | -1 | -1 | -1 | +1 | +1 |

| 7    | +1     | -1 | -1 | +1 | -1 | +1 | +1 | -1 |

Table 3.1: Functions for sender nodes

C) For the simultaneous transmission of four messages, the Walsh functions shown in Table 3.1 shall be used. The nodes 0, 3, 6, and 7 transmit data according to the Table 3.2. Give the resulting signal on the media, make use of the given scheme in Table 3.2.

| Node            | Data | Signal |  |  |  |  |  |

|-----------------|------|--------|--|--|--|--|--|

| 0               | "1"  |        |  |  |  |  |  |

| 3               | "0"  |        |  |  |  |  |  |

| 6               | "1"  |        |  |  |  |  |  |

| 7               | "0"  |        |  |  |  |  |  |

| Signal on media |      |        |  |  |  |  |  |

Table 3.2: Transmission with CDMA

Matr.-Nr.: 1234567

ID: 1

D) The following Signal has been received from a transmission using all the eight Walsh functions from this task.

$$+1.1 + 2.8 + 2.4 + 2.0 - 1.8 + 4.3 - 1.0 - 0.7$$

As corruptions might happen during transmission, the receiver has a tolerance band for the detection. All values differing up to  $\pm 0.5$  from the ideal value will still be accepted. Calculate the bit value that the receiver will detect for node 2, and node 4.

Matr.-Nr.: 1234567 ID: 1

#### **Media Access** Task 4:

#### Task 4.1: **Multiple Access**

Eight different devices communicate on a shared bus-system using TDMA with static time-slot assignment. It can be assumed, that the clocks of each node are perfectly synchronized using a separate clock wire (i.e. clock wire delays are completely compensated). On the data wire, only payload data needs to be transmitted without any additional synchronization overhead. The TDMA cycles (time frames) last for  $t_f = 5ms$  and contain exactly one time-slot for each of the 8 participants. The physical signal propagation delay (one-way delay) between the two most distant nodes on the bus is  $\Delta_{max} = 50 \mu s$ . All TDMA time-slots are of equal length and each symbol has a fixed duration of  $t_{sym} = 2.5 \mu s$ .

| A) | To avoid symbol interference, a guard interval is inserted at the end of each time-slot. How           |

|----|--------------------------------------------------------------------------------------------------------|

|    | long should this guard interval be at least in order to fully prevent symbol interference in           |

|    | the given system? Calculate the length of the time-slots $t_{sl}$ as well as the time $t_{send}$ which |

|    | can be used for data transmission during a time-slot.                                                  |

| B) | Some of the devices may need to transmit larger amounts of data which can take several                |  |

|----|-------------------------------------------------------------------------------------------------------|--|

|    | seconds. Calculate the average baud-rate $f_s$ that can be achieved for such transmissions.           |  |

|    | (If you did not solve the previous question, assume that in each time-slot $t_{send} = 605 \mu s$ can |  |

|    | be used for data transmission )                                                                       |  |

## Task 4.2: CSMA/CA

A communication system comprises five communication nodes that use CSMA/CA as arbitration scheme. In order to transmit data a node transmits a dominant start bit  $(,0^{\circ})$  for synchronization purpose. After that a 5 bit message identifier followed and 10 bits of payload data is sent. The message identifiers are unique for each node and all data is sent MSB first. The bus has to cover a maximum distance of 500m.

| A) | Which requirements have to be fulfilled in order to guaranty a faultless function of the |  |

|----|------------------------------------------------------------------------------------------|--|

|    | system? What are the implications for the transmission rate?                             |  |

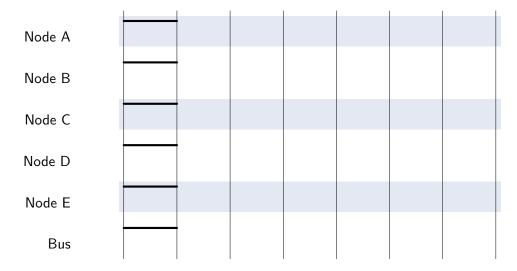

B) Table 4.1 shows the identifier of each node. Perform the arbitration phase and fill out the timing diagram in Figure 4.1.

| Node         | identifier |

|--------------|------------|

| A            | 10011      |

| В            | 11001      |

| $\mathbf{C}$ | 11010      |

| D            | 10100      |

| ${ m E}$     | 10100      |

Table 4.1: Specification of nodes

Figure 4.1: Bus Access

C) Which node is granted exclusive access to the bus?

### Task 4.3: Arbitration

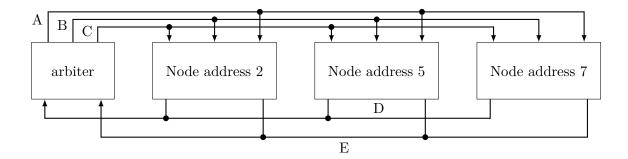

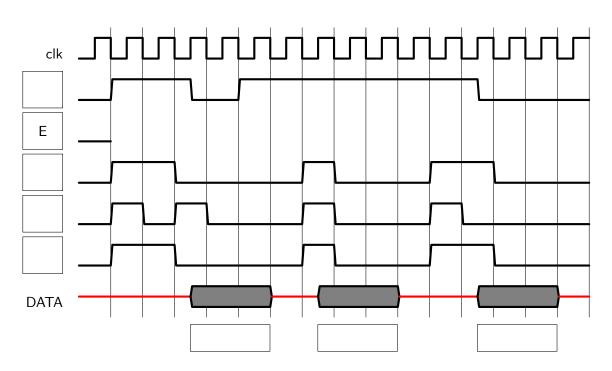

A system using polling is shown in Figure 4.2. An exemplary arbitration cycle of the system is shown in Figure 4.3. Signal E is the busy line.

A) Assign the correct signal lines of Figure 4.2 to the signals shown in the diagram below (Figure 4.3). Justify your choice of signal line assignment with a few sentences. What node is sending data at which point in time? Complete the diagram (Figure 4.3) accordingly and in addition draw the signal line E.

Figure 4.2: Polling

Figure 4.3: Signal flow for Polling

| D: 1 |

|------|

| ĺ    |

# **Task 5: Error Protection**

# Task 5.1: Multiple Choice

A) Specify whether the statements in table 5.1 are true or false.

Hint: Wrong answers will be penalized. No answer will not give any positive or negative points. The task will be evaluated with a minimum of 0 points.

| Statements                                                                            | True | False |

|---------------------------------------------------------------------------------------|------|-------|

| The receiver has to use the same CRC generator polynomial as the sender               |      |       |

| All single-bit errors are detectable with CRC                                         |      |       |

| All error bursts > degree of the CRC generator polynomial are detectable              |      |       |

| The error flag (primary) in CAN bus communication is one bit long                     |      |       |

| A CAN bus communication node switches into error mode if RX CNT is higher than TX CNT |      |       |

| Security is the protection against malicious errors caused by attackers               |      |       |

Table 5.1: Multiple Choice

### Task 5.2: CRC-Calculation

| A) | To protect data transmission in a mobile device, the given CRC generator polynomial  |  |

|----|--------------------------------------------------------------------------------------|--|

|    | should be implemented. Draw the short form of the linear feedback registers with XOR |  |

|    | operators for the given generator polynomial.                                        |  |

|    | Given CRC generator polynomial: $x^7 + x^6 + x^5 + x^2 + 1$                          |  |

| wing hit stream is to be   | Calculate the data stream that will be transmitted if the fo                                                                                                                                                                                                        |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Calculate the data stream that will be transmitted if the for protected using the CRC generator polynomial given in task 5 Data stream for transmission: 1010 1011                                                                                                  |

|                            |                                                                                                                                                                                                                                                                     |

| uming that the generator   | In a transmission system that uses CRC for error detection, a rebitstream: 1110 1001 0101 Carry out the CRC error detection scheme of the receiver, a polynomial $x^4 + x^3 + x^2 + 1$ has been used to generate the chedoes the receiver conclude from the result? |

| nas occurred in the trans- | Specify the correct bit stream, assuming that only one bit erromitted bitstream of the task 5.2 C).                                                                                                                                                                 |

### Task 5.3: CAN Bus

| A) | What are the two main tasks of the ARB Field in a CAN Bus message? |  |

|----|--------------------------------------------------------------------|--|

|    |                                                                    |  |

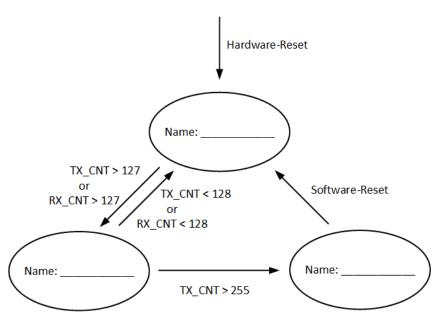

B) In figure 5.1 the error states of the CAN bus communication is shown. Please, fill in the names of the states correctly.

Figure 5.1: CAN Error States

C) In a fresh restarted CAN bus communication system only one node acts as sender and transmits a CAN message every 20 ms. Assume that in every 2nd transmission the sender does not receive an ACK (without a following error flag). Assume further that the first successful transmission is done at t=0 ms. How long does it take until the sender node switches into the Error Passive state?

# Task 6: Protocols

### Task 6.1: FireWire Arbitration

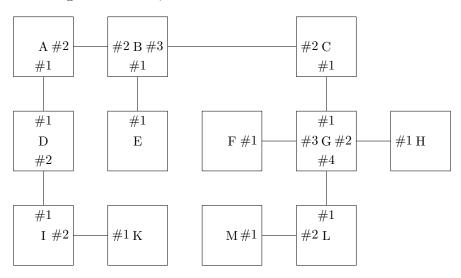

The FireWire network shown below is given. The complete self-configuration of the network is already done including initialization, tree identification and self identification.

Figure 6.1: FireWire network

Now a normal FireWire bus cycle should be considered. For simplification, several assumptions should be taken into account:

- A list of nodes wanting to send is given.

- All nodes start requesting the bus at the same time.

- Processing of arbitration requests are done in zero time. There are no delays for propagation of the arbitration decision.

- If a node receives multiple bus requests, it will always forward the request that it receives from the port with the lowest number.

| A) | Mark the root of the FireWire Network in Figure 6.1!  The following nodes request access to the bus: <b>A</b> , <b>B</b> , <b>C</b> , <b>E</b> , <b>H</b> . Determine the order in which the nodes will be granted access to the bus. |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B) | If the root sends continuously, it would always grant access to the bus. How does FireWire preserve fairness? Explain your answer for multiple sending nodes <b>and</b> only root sending!                                            |  |

|    |                                                                                                                                                                                                                                       |  |

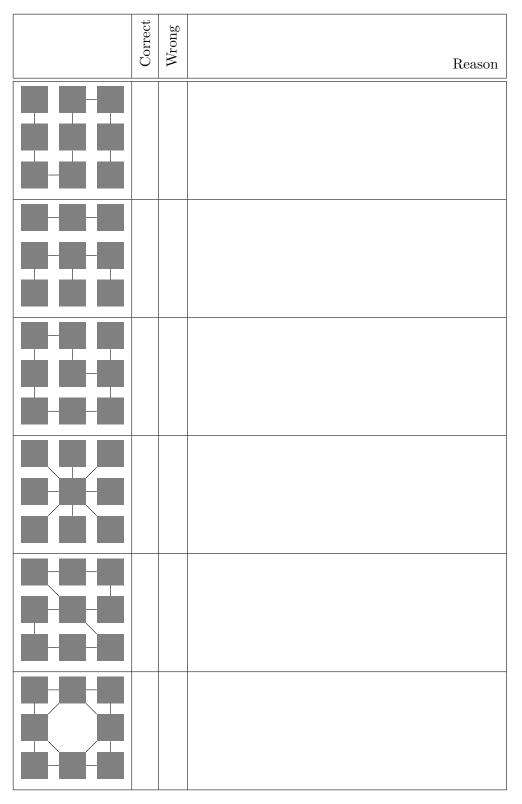

### Task 6.2: FireWire Structures

A) Different FireWire structures were built during a student laboratory. During test phase you notice that not all FireWire systems are working. Please state if the FireWire systems given below are working correctly. Mark the roots, if the systems are correct. Give a reason, if the FireWire system is not working correctly.

Table 6.1: FireWire structures

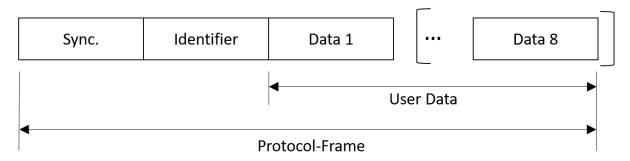

### Task 6.3: ITIV-Protocol

The following protocol is used to transfer data between a PC and three wireless weather stations.

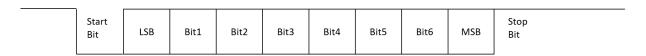

The protocol is based on a simple serial data transfer. The transferred data is divided into blocks according to functionalities (Figure 6.2), with the exception of synchronisation (Sync.) with 12 low bits, followed by a high bit. All others follow the rules in Figure 6.3 and Figure 6.4, the exact overview is given below.

Figure 6.2: Structure of a protocol frame

Figure 6.3: Bit sequence within a block

Figure 6.4: Structure of the identifier field

A) Draw the structure of the wireless network! What kind of topology (analogous to wired structures) is the network?

| Mat | ID: 1                                                                                                                                                                                   |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B)  | Use the protocol to determine the maximum number of slaves that can be addressed within a network. Justify your answer!                                                                 |  |

| C)  | How many bits does a transmission from the master to the slave with the address $0x02$ take, if 4 user bytes are sent?                                                                  |  |

| D)  | A datastream consisting of the same bits as the "sync." should be transmitted. Do you need to modify the protocoll in order to transmit this data? If Yes: Explain how! If no: Why not? |  |

| bars. Describe the differences between both in terms of hardware resources and routing capabilities.                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bars. Describe the differences between both in terms of hardware resources and routing capabilities.                                                 |

| bars. Describe the differences between both in terms of hardware resources and routing capabilities.                                                 |

| C) Describe a reasonable way to implement the routing control and message buffers of a router.                                                       |

| C) Describe a reasonable way to implement the routing control and message buffers of a router.                                                       |

|                                                                                                                                                      |

| D) Describe the implications of circuit and packet switching to the routing control and message buffers of a router? How are they different and why? |

## Task 7.2: Routing

A) Name and describe 2 categories that can be used to classify routing algorithms!

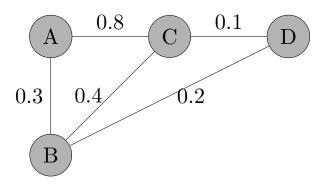

Figure 7.1: Given network topology

B) Figure 7.1 represents a network for which an optimal routing has to be found. The weights represent the error rate of each connection. With node A as the starting point, calculate the paths with the lowest error rates in the network by using Dijkstra's algorithm. For that write down the order in which nodes are visited in each bracket under the current step and fill out the given tables that encompass the shortest paths after each visitation of a node.

|        | step 1   |       | step 2 |       | step 3 |       | step 4 |       | step 5 |       |

|--------|----------|-------|--------|-------|--------|-------|--------|-------|--------|-------|

| node   | A        |       |        |       |        |       |        |       |        |       |

| vertex | err.     | pred. | err.   | pred. | err.   | pred. | err.   | pred. | err.   | pred. |

| A      | $\infty$ | A     |        |       |        |       |        |       |        |       |

| В      | $\infty$ | -     |        |       |        |       |        |       |        |       |

| C      | $\infty$ | -     |        |       |        |       |        |       |        |       |

| D      | $\infty$ | -     |        |       |        |       |        |       |        |       |

Table 7.1: Dijkstra's algorithm

| Mat | rNr.: 1234567 ID: 1                                                                                                                                         |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| C)  | Describe a scenario in which the connection between the nodes A and C from Figure 7.1 would be preferable, compared to a connection with lower error rate ! |  |

|     |                                                                                                                                                             |  |

| D)  | Describe a scenario and explain why the Dijkstra algorithm is more suitable for routing than XY-Routing!                                                    |  |

|     |                                                                                                                                                             |  |

|     |                                                                                                                                                             |  |

# **Task 8: Network Topologies**

### Task 8.1: General Questions

A) There are four topologies given: 4x2x2 Mesh, 4x4 Torus, Star, Ring. Assume that each topology contains 16 nodes. Give the value of edge connectivity, diameter and resource cost(i.e. in this case the total number of bi-directional links). Use the following table to provide your answers.

| Network    | Edge<br>Connectivity | Diameter | Resource Cost |

|------------|----------------------|----------|---------------|

| 4x2x2 Mesh |                      |          |               |

| 4x4 Torus  |                      |          |               |

| Star       |                      |          |               |

| Ring       |                      |          |               |

Table 8.1: Metrics and topologies

## Task 8.2: 4D Topology

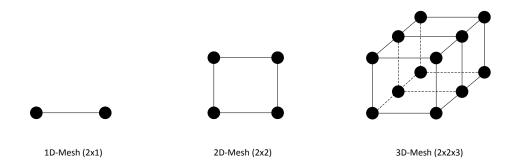

When we increase the amount of nodes in a mesh, it can be useful to scale the mesh into a higher dimension instead of adding the nodes in the same dimension. A higher dimension keeps the diameter low while increasing the edge connectivity of the nodes.

Figure 8.1: Drawing higher-dimensional meshed networks

For drawing higher dimensional mesh topologies on a sheet of paper, some techniques exist. If we consider a 1-dimensional topology consisting of two nodes and want to move towards a 2-dimensional (2x2) topology, we simply copy our original nodes and connect each node with their exact copy. For a 2x2x3 topology, we copy the existing 2x2-rectangle two times (resulting in 3 rectangles) and connect each original node with their first copy and their first copy with the second copy. The same technique can be applied to a 4D topology, where we copy our 3D cubes and connect each node to its next copy.

Assume a 4x2x5x3 mesh topology for this task. Each node can be described by the tuple  $(x_1,x_2,x_3,x_4)$ . Find the shortest path from the source point (4,0,2,3) to the destination point (1,1,3,1). Thereby, the routing policy that each node has to obey is described as follows: 1. Try first to route in the direction of the largest vector component from the current router's position towards the destination. The vector components are  $\|\Delta x1\|$ ,  $\|\Delta x2\|$ ,  $\|\Delta x3\|$ ,  $\|\Delta x4\|$ . 2. In case there are multiple directions with the same largest value for the respective vector components possible, prioritize first x1 then x2 then x3 and finally x4 among the directions with the largest vector components. In your answer please name all traversed nodes (i.e. their coordinates) in the correct sequence. A fault is now present in the router at node (1,1,2,1). Due to this fault the router behaves as described below. 1. The router tries to route in the direction of the largest vector component from the current router's position away from the destination. The vector components are  $\|\Delta x1\|$ ,  $\|\Delta x2\|$ ,  $\|\Delta x3\|$ ,  $\|\Delta x4\|$ . 2. In case there are multiple directions with the same largest value for the respective vector components possible, prioritize first x1 then x2 then x3 and finally x4 among the directions with the largest vector components. The other routers in the network are not aware of the fault in this router and will perform the routing without changing their strategies. Now route a packet starting from (4,1,2,1)towards (1,1,3,1) and name all visited nodes. Does the packet still reach its destination even with the faulty router? Explain your answer.

Matr.-Nr.: 1234567

ID: 1

| Ma         | trNr.: 1234567                                                             | ID: 1 |  |

|------------|----------------------------------------------------------------------------|-------|--|

| C)         | Explain the difference between a livelock and a deadlock in a network.     |       |  |

|            |                                                                            |       |  |

|            |                                                                            |       |  |

|            | What is the edge connectivity and the diameter of a 4x2x5x3 mesh topology? |       |  |

| <i>D</i> ) | what is the edge connectivity and the diameter of a 4x2x3x3 mesh topology: |       |  |

|            |                                                                            |       |  |

|            |                                                                            |       |  |